Page 85 - Vol.08

P. 85

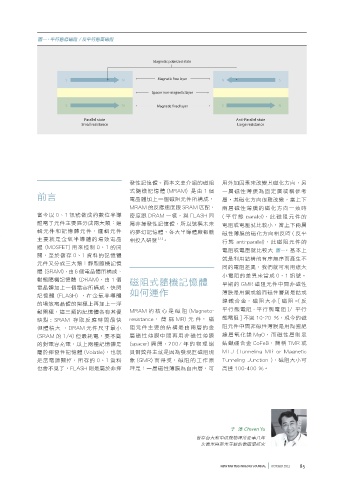

圖一、平行態低磁阻 / 反平行態高磁阻

Magnetic polarized state

S N Magnetic free layer N S

Spacer non-magnetic layer

S N Magnetic xed layer S N

Parallel state Anti-Parallel state

Small resistance Large resistance

Introduction

發性記憶體。而本文要介紹的磁阻 用外加因素來改變其磁化方向,另

式隨機記憶體 (MRAM) 是由 1 個 一層磁性薄膜為固定層或稱參考

前言 電晶體加上一個磁阻元件所構成, 層,其磁化方向很難改變,當上下

MRAM 的反應速度跟 SRAM 匹配, 兩層磁性薄膜的磁化方向一致時

當今以 0、1 訊號做成的數位半導 密度跟 DRAM 一樣,與 FLASH 同 ( 平 行 態 parallel), 此 磁 阻 元 件 的

體電子元件主要區分成兩大類:邏 屬非揮發性記憶體,所以號稱未來 電阻或電壓就比較小,當上下兩層

輯元件和記憶體元件,邏輯元件 的夢幻記憶體,各大半導體廠都競 磁性薄膜的磁化方向相反時 ( 反平

主要就是金氧半導體的場效電晶 相投入研發 [1] 。 行態 anti-parallel),此磁阻元件的

體 (MOSFET) 用來控制 0、1 的開

電阻或電壓就比較大 圖一,基本上

關,至於儲存 0、1 資料的記憶體

就是利用結構的有序無序而產生不

元件又分成三大類:靜態隨機記憶

同的電阻差異,我們就可利用這大

體 (SRAM),由 6 個電晶體所構成、

小電阻的差異來當成 0、1 訊號。

動態隨機記憶體 (DRAM),由 1 個 磁阻式隨機記憶體

電晶體加上一個電容所構成、快閃 如何運作 早期的 GMR 磁阻元件中間非磁性

記憶體 (FLASH) ,在金氧半導體 薄膜是用銅或鉻而磁性層則是鈷或

鎳鐵合金,磁阻大小 [ 磁阻 =( 反

的場效電晶體的閘極上再加上一浮

動閘極,這三類的記憶體各有其優 MRAM 的 核 心 是 磁 阻 (Magneto- 平行態電阻 - 平行態電阻 )/ 平行

缺點 : SRAM 存取反應時間最快 resistance, 簡 稱 MR) 元 件, 磁 態電阻 ] 不過 10-20 %,現今的磁

但體積大 ,DRAM 元件尺寸最小 阻元件主要的結構是由兩層的金 阻元件中間非磁性薄膜是用陶瓷絕

(SRAM 的 1/4) 但最耗電,要不斷 屬磁性薄膜中間再用非磁性薄膜 緣層氧化鎂 MgO,而磁性層則是

的對電容充電,以上兩種記憶體是 (spacer) 隔 開,2007 年 的 物 理 諾 鈷鐵硼合金 CoFeB,簡稱 TMR 或

屬於揮發性記憶體 (Volatile),也就 貝爾獎得主就是因為發現巨磁阻現 MTJ (Tunneling MR or Magnetic

是當電源關掉,所存的 0、1 資料 象 (GMR) 而得獎,磁阻的工作原 Tunneling Junction ),磁阻大小可

也會不見了,FLASH 則是屬於非揮 理是:一層磁性薄膜為自由層,可 高達 100-400 %。

于 淳 Chwen Yu

曾在台大和中研院物理所從事八年

次微米與奈米等級的微磁學研究

NEW FAB TECHNOLOGY JOURNAL OCTOBER 2012 85