Page 48 - Vol.25

P. 48

Tech

Notes

技術專文

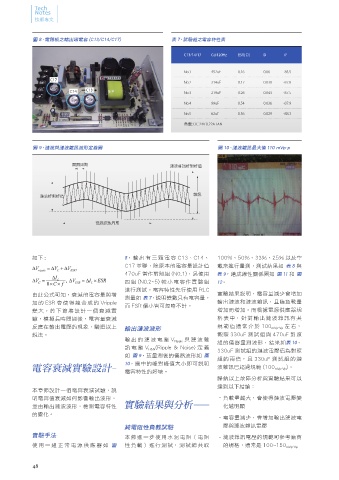

圖 8、電路板之輸出端電容 (C13/C14/C17) 表 7、試驗組之電容特性表

C13/14/17 C@120Hz ESR(Ω) D θ

No.1 452uF 0.16 0.06 -85.5

C17

No.2 314uF 0.17 0.038 -87.8

C14 C13 No.3 219uF 0.26 0.043 -87.5

No.4 99uF 0.54 0.036 -87.9

No.5 62uF 0.56 0.029 -88.3

負載: DC 24V 0.22A FAN

圖 9、漣波與漣波雜訊波形定義圖 圖 10、漣波雜訊最大值 110 mVp-p

開關周期 漣波雜訊峰對峰值

漣波峰對峰值 雜訊

電源訊號周期

如下 : 8, 輸 出 有 三 顆 電 容 C13、C14、 100%、50%、33%、25% 以及空

C17 並聯,除原本的電容量設計值 載來進行量測,測試結果如 表8 與

470uF 當作對照組 (N0.1),另使用 表9,繪成線性關係圖如 圖 11 和 圖

四組 (N0.2~5) 較小電容作實驗組 12。

進行測試。電容特性先行使用 RLC

由此公式可知,衰減的電容量與增 實驗結果說明,電容量減少會增加

測量如 表7 ,說明變數只有電容量,

加的 ESR 會使得總合成的 Vripple 輸出漣波和漣波雜訊,且隨負載量

而 ESR 偏小皆可忽略不計。

變大。於下節將設計一個衰減實 增加而增加。而根據電源供應器規

驗,模擬長時間過後,電容量衰減 格表中,針對輸出漣波雜訊有其

反應在輸出電壓的現象,驗證以上 輸出漣波波形 規範值通常介於 100 mVp-Vp 左 右,

說法。 觀察 330uF 測試組與 470uF 對照

輸出的漣波電壓 V Ripple 與漣波雜

組的儀器量測波形,結果如表 10,

訊電壓 V R&N (Ripple & Noise) 定 義

330uF 測試組的漣波電壓值為對照

如 圖9,茲量測後的儀器波形如 圖

組的兩倍,且 330uF 測試組的漣

10,圖中的峰對峰值大小即可說明

電容衰減實驗設計 波雜訊已超過規範 (100 mVp-Vp )。

電容特性的好壞。

歸納以上故障分析與實驗結果可以

達到以下結論:

本章節設計一個電容衰減試驗,說

明電容值衰減如何影響輸出波形, – 負載量越大,會使得漣波電壓變

並由輸出漣波波形,檢測電容特性 實驗結果與分析 化越明顯

的變化。

– 電容量減少,會增加輸出漣波電

純電阻性負載試驗 壓與漣波雜訊電壓

實驗手法 本節進一步使用水泥電阻(電阻 – 漣波雜訊電壓的規範可參考廠商

使用一組正常電源供應器如 圖 性負載)進行測試,測試總共取 的規格,通常是 100~150 mVp-Vp

48