摘要

先進封裝廠務品質發展藍圖

Keywords / Advanced Packaging,Facility Quality,Technology Roadmap2,RDL,ITRS2,Model For Quality Management

前言

先進封裝廠務品質藍圖的必要性

摩爾定律作為電子製造產業鏈的金科玉律,一直屹立於科技發展的前沿,給整個電子製造產業鏈指明非常明晰的發展方向。但近些年,由於IC製造過程中使用的黃光微影技術(Photolithography)相對於摩爾定律顯得相對滯後 ,IC業界給予厚望的EUV(Extreme UltraViolet)黃光設備,技術成熟度雖已達量產的水平,但良率仍待提升,使得IC製造成本在技術節點不斷縮小的情況下,成本呈現指數增長;另一方面,2019年蘋果A13晶片、AMD EPYC Rome、驍龍865、麒麟810等產品蓄勢待發,晶圓節點已經發展到7nm量產的階段,非常接近FinFET製程的物理極限,即便EUV設備已經可以量產使用,也無法改變摩爾定律即將抵達終點的趨勢。那接下來電子製造行業該何去何從?

業界和學界給出了比摩爾定律更為多元化的答案 :「More Moore(深度摩爾)」IC製造角度的摩爾定律和「More than Moore(超越摩爾)」IC封裝角度的摩爾定律。進一步來說,CMOS微縮將繼續下去,明顯提升的參數卻只有密度,而成本、功耗和性能增益均低於期待。半導體產業協會更明確指出,異質整合(封裝技術)是唯一能夠讓摩爾定律在未來數十年持續進展的解決方案[20]。

在2016年,台積電利用自行所開發的扇出型晶圓級封裝(InFO FOWLP, Integrated Fan Out Wafer-Level Pack-age)為客戶生產封裝新一代智慧型手機所需的處理器。此舉備受全球業界的注目,同時刺激了全球各大半導體企業加速FOWLP封裝技術的開發,並確立台積電在先進封裝產業先行者的地位。而不同於半導體前段製程,鮮少有先進封裝廠務品質相關的研究文獻可供參考,在封裝業越趨微利以及技術發展不斷加速的時空背景下,如何建立具有競爭力,並滿足製程快速發展需求的先進封裝廠務品質發展藍圖,是本文主要研究的課題。

先進封裝廠務供應品質現況

相較於其他的封裝業者,由傳統封裝導入先進封裝製程,台積電是由半導體製造廠切入先進封裝製造。我們提供接近半導體製造等級的廠務品質,供應先進封裝製程生產。目前共有三個先進封測廠,Pilot Line分別源自不同半導體廠 :

封測A廠 :

源於12吋晶圓廠發展的甲製程。

封測B廠 :

源於8吋晶圓廠發展的乙製程。

封測C廠 :

源於6吋晶圓廠發展的丙製程。

基本上,廠務供應系統皆以母廠Pilot Line半導體製造等級的廠務品質作為建廠設計參考,並未因應先進封裝製程特性需求,量身打造廠務系統,換句話說,先進封裝尚未發展出自身的廠務品質標準。舉一個實際案例,為了搭配先進製程微縮及異質晶片整合趨勢,2018年台積電推出整合多晶片的封裝技術(丙製程),在封測C廠建置量產的產線,但因母廠(六吋廠)P-line由UPW中段系統供應生產,並未明訂水質標準,故為此召開丙製程水質制定會議。 FAC、QR、PE、BID等與會單位一直無法取得共識,主因為廠務提出水質標準並無理論依據,無法說服其他與會單位,故希望能以高度相關的理論及文獻為依據,作為未來新製程制定廠務品質標準的基準。

先進封裝廠務需求與挑戰

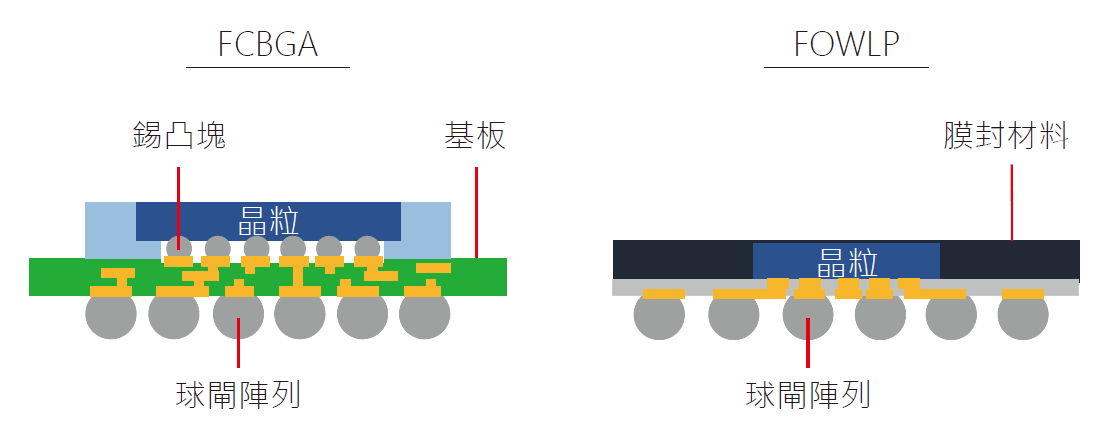

近年來,先進封裝製程重大革新當屬扇出型晶圓級封裝(FOWLP)量產,相較於傳統覆晶封裝(FCBGA),扇出型晶圓級封裝以重佈線層(RDL)取代傳統載板,大幅降低厚度及成本→圖1。在晶圓的製程中[24],從半導體裸晶的端點上,拉出所需的電路到RDL,進而形成封裝。在這樣的基礎上就不需要封裝載板,更不用打線(Wire)以及凸塊

(Bump),進而得以降低30%的生產成本,以及減少晶片的厚度。Fan-Out WLP除了滿足不斷增加的I/O數的需求外,最大的特點就是其採用RDL代替了傳統IC封裝所需的IC載板,從而大大降低了整體封裝厚度,這一點極大地滿足了智慧型手機對厚度的要求。

圖1、 FOWLP封裝技術的簡略示意圖[2]

根據Yole Development統計數據[23],扇出型封裝市場預計至2021年將由台積電的高密度封裝佔據7成市場佔比,需求將由手持式產品、物聯網消費性產品、車用電子、高速運算處理器四大領域驅動。產品之複雜度遽增情況下 ,能選擇的晶片封裝方式亦逐漸受限,皆須先進封裝製程,這主要是因為高效能產品搭配先進製程晶片,同時需高度整合之封裝技術。

半導體晶片微縮下,RDL將晶片上極高密度的I/O點,連接到基板密度極低的I/O,需要更多層以匹配晶片的線密度,這反過來增加了整個封裝的成本。Lam Research的先進封裝副總裁Choon Lee 表示,向更新的高端封裝解決方案的轉變,推動了增加的資本支出,這可能會成為封裝廠的挑戰[16]。因此,要如何提升效能之餘,同時降低成本,Ultratech副總Warren W. Flack 提出兩者兼得的方案,發展更細線寬的RDL,有助於減少重佈線層數量,降低封裝成本[26]。

為了形成RDL,必須於先進封裝製程(簡稱後段製程)導入半導體製造技術(簡稱前段製程),因此也打破了固有前段製程與後段製程藩籬[6]。因此,對於未來的半導體世界來說,決勝手段已不是僅僅只是在5奈米或3奈米製程的微縮能力,而是已經延伸到考量前後段製程一貫性的異質整合。對於廠務品質而言,傳統封裝的廠務品質已經無法滿足先進封裝製程的需求,台積電做為先進封裝產業的先行者,面對無前例可循,及沒有研究文獻可供參考的窘境,如何訂定未來先進封裝廠務品質是一大挑戰。

系統化的先進封裝廠務品質管理

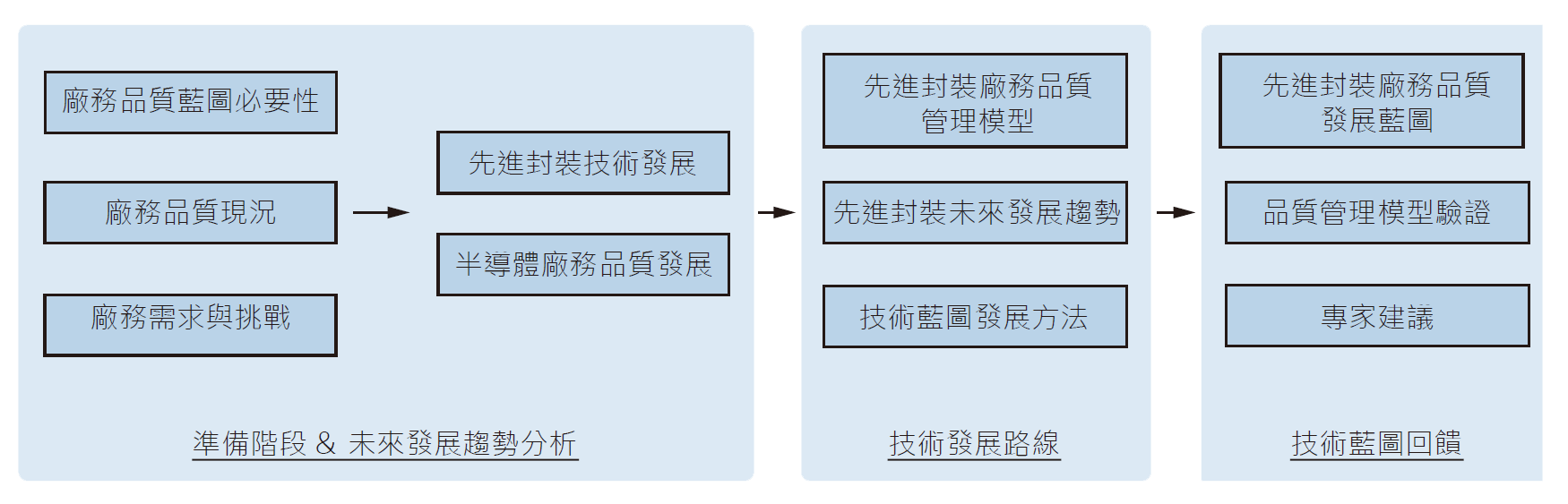

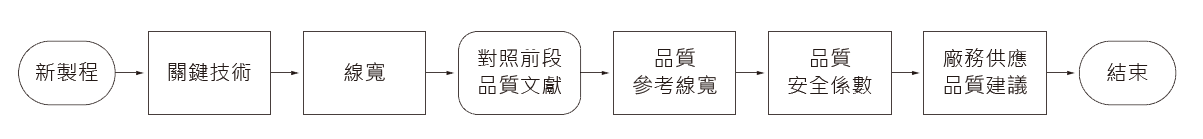

半導體製造廠務品質,均參照國際半導體技術發展藍圖(International Technology Roadmap for Semiconduc-tors, ITRS)訂定品質標準,但先進封裝目前並無相關藍圖文獻可供參考。余振華副總表示「台積電將移植半導體發展經驗,全力打造先進封裝技術。」台積電作為先進封裝業的先行者,同時兼具半導體製造經驗的競爭優勢。因此,先進封裝廠務品質亦可參考半導體的發展經驗,配合先進封裝製程特性,發展先進封裝廠務品質藍圖,進而建構系統化的先進封裝廠務品質管理。根據國際能源署[10]及Power Chip Semiconductor Manufacturing Corporation [17]提出建構技術路線圖的4個階段 : 準備、未來發展趨勢分析、技術發展路線、技術路線圖回饋。以此四階段發展先進封裝廠務品質藍圖→圖2。

圖2、研究方法

文獻探討

先進封裝技術發展

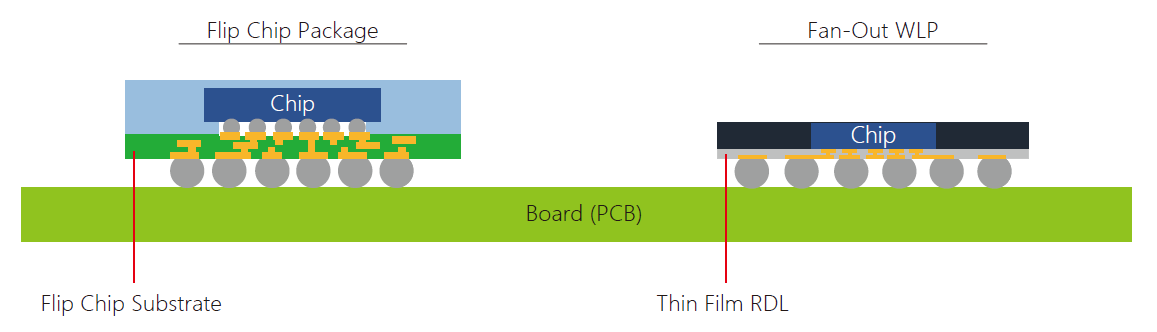

先進封裝技術發展,起源於1960年代的覆晶封裝(Flip Chip)技術,而扇出型封裝技術主要源於2008年意法半導體 、英飛凌開發之嵌入式晶圓級球閘陣列(Wafer-Level Ball Grid Array, eWLB)。現今之覆晶封裝技術較扇出型成熟 ,具備晶片整合之覆晶封裝(Flip Chip Ball Grid Array, FCBGA)面積大於55*55mm² 以上,同時I/O數大於3000個以上,主要以GPU、HBM等等需要大量運算晶片使用;而扇出型封裝目前仍以單一晶片封裝為主,封裝尺寸小於15*15mm²,同時I/O數小於1500個,主要以手機通訊等相關應用為主。近年來,更發展出以RDL及薄膜取代載板(Substrate)的技術→圖3。

圖3、覆晶封裝及扇出型封裝比較[7]

Yole Development研究[23]指出,傳統覆晶封裝(Flip Chip)、目前發展快速的扇出型、2.5D及3D封裝技術等,其2015年至2021年之產值年複合成長率分別為5%、49%及43%;相對新技術的快速成長,產量及產值最大的覆晶封裝技術成長率確實遜色許多,此亦反應覆晶封裝之載板不論在整合度,亦或在價格上都存在著技術瓶頸。因此 ,電子產品對於高頻寬及高速運算需求,將帶動扇出型封裝,甚至更高階之2.5D及3D封裝發展。

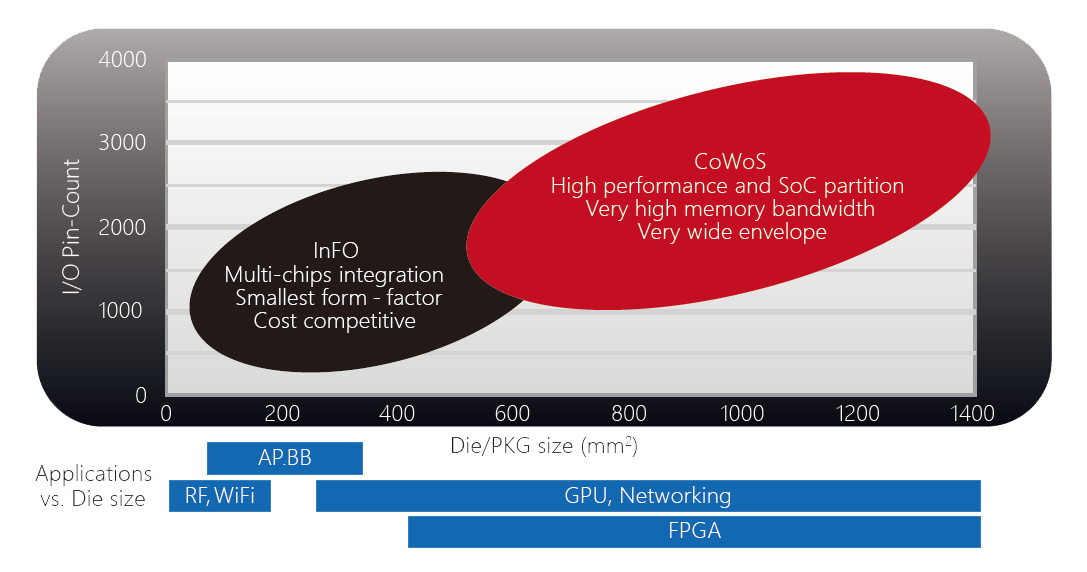

因此,近年來台積電陸續投入研發扇出型封裝,2.5D及3D等高階封裝技術,包括CoWoS(Chip on Wafer on Substrate)及InFO(Integrated Fan-Out)。CoWoS針對高端市場,連線數量和封裝尺寸都比較大,InFO針對性價比市場,封裝尺寸較小,連線數量也比較少→圖4。其共通點都是在半導體製造完成後即進行封裝,並可將多顆晶片整合堆疊放在單一的元件上,再封裝在基板上,省時又省成本。

圖4、InFO & CoWoS技術比較[2]

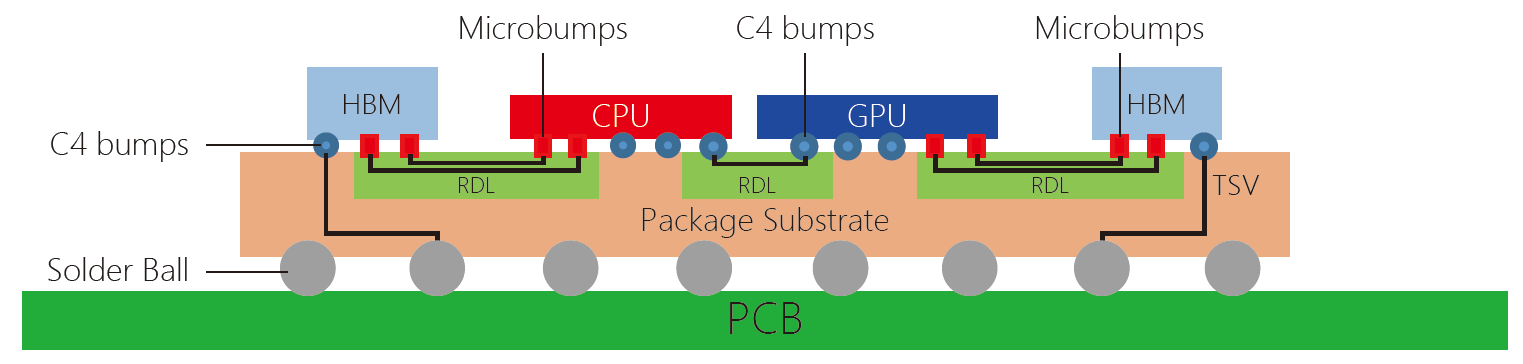

CoWoS為大尺寸且多接點的晶片封裝技術,先於半導體廠完成重佈線層(RDL)及矽穿孔(TSV)製程,再由先進封裝廠以C4 Bump、MicroBumps(簡稱μBump)連接,整合而成CoW-on-Substrate,結構→圖5。

圖5、CoWoS 產品示意圖[22]

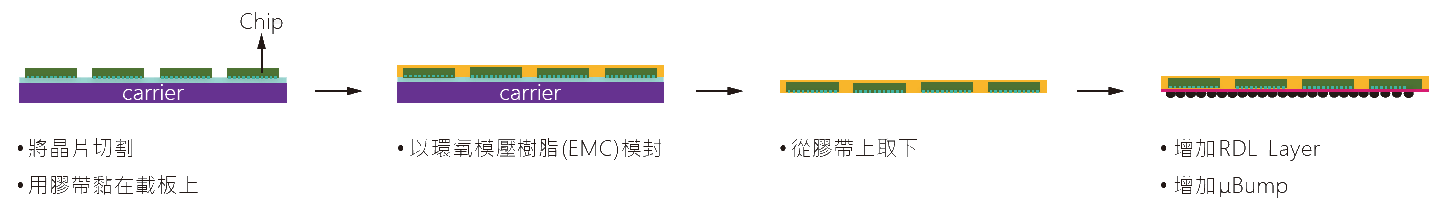

而InFO 為小尺寸且成本低的終端電子產品封裝製程,以模封、μBump及Cu-RDL取代傳統載板,詳細流程→圖6。

圖6、InFO簡易製程介紹[1]

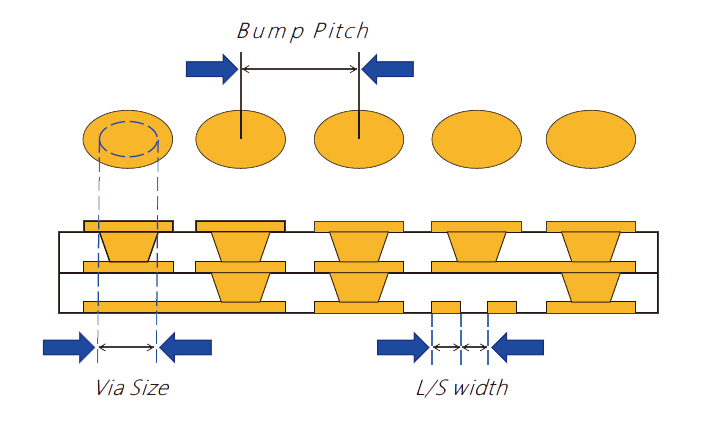

一般而言,這兩種製程所需之關鍵技術相差不大,根據文獻[4][25]歸納三大關鍵技術的線寬做為衡量技術能力→表1、圖7,分別為 :

|

Key technology components |

2017 |

2018 |

Qualified |

Advance |

Reference |

|

|---|---|---|---|---|---|---|

|

InFO |

Bump Pitch |

0.4mm |

NA |

171µm |

130µm |

ASE FOWLP Roadmap (2017) |

|

Cu-RDL(L/S) |

15/15µm |

2/2.5µm |

2/2µm |

|||

|

Via Opening |

20µm |

15µm |

10µm |

|||

|

CoWos |

C4 Bump |

NA |

130µm |

NA |

Applied Physics Reviews 2, 021308 (2015), TSMC 2018 Technology Symposium |

|

|

Solder ubump Pitch |

10µm |

|||||

|

*CoWoS RDL(0.5µm), TSV(12µm)為Foundrey Levl製程,由前段廠製作。 |

||||||

圖7、先進封裝關鍵技術示意圖[4]

Opening Via Size :

DRAM連接與IC晶片處開孔大小。

Cu-RDL 線寬(L/S Width) :

連通DRAM及IC晶片的線寬。

Bump Pitch :

IC晶片連接PCB板或載板的球大小,如球柵陣列封裝(Ball Grid Array, BGA), C4 Bump, μBump等。

而其中以RDL為先進封裝最精細的技術,彙整目前台積電先進封裝廠的製程關鍵技術及線寬→表2 :

|

先進封裝廠區 |

主要製程 |

關鍵技術 |

線寬 |

|---|---|---|---|

|

封測A廠 |

製程甲 |

RDL |

2 µm |

|

C4 Bump |

130 µm |

||

|

Via Opening |

10µm |

||

|

封測B廠 |

製程乙 |

MicroBump |

10 µm |

|

C4 Bump |

130 µm |

||

|

封測C廠 |

製程丙 |

C4 Bump |

130 µm |

封測A廠:

甲製程的RDL線寬為2μm。

封測B廠:

乙製程的μBump 線寬為10μm(RDL線寬為0.5μm於半導體廠製造)。

封測C廠:

丙製程的C4 Bump線寬為130μm。

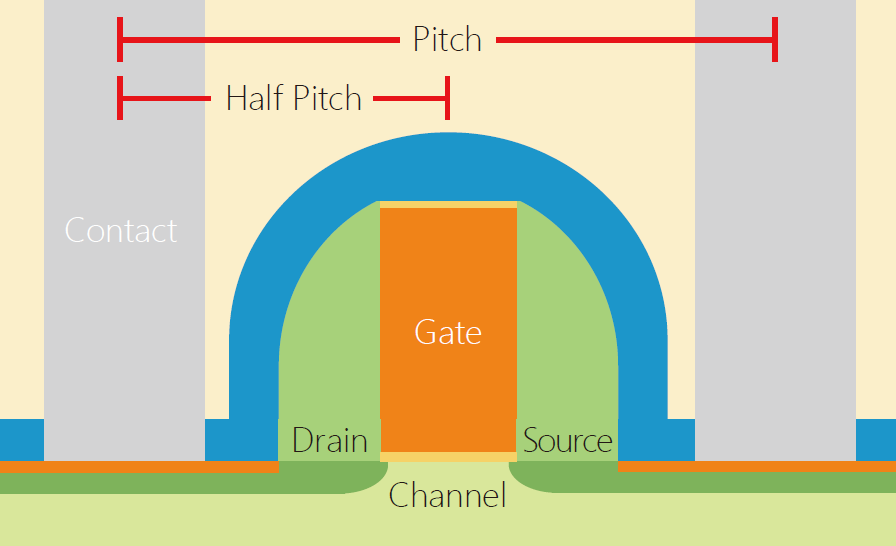

半導體廠務品質發展

半導體發展歷史遵循著名的摩爾定律,每18個月電晶體密度提升一倍。為集中全世界研發能力,避免因各自發展造成資源錯置,1992年起半導體協會(Semiconductor Industry Association, SIA)廣邀各界制定國際半導體技術發展藍圖(International Technology Roadmap for Semiconductors, ITRS)。至2017年,國際半導體技術發展藍圖(ITRS)不再更新,由國際裝置與系統發展路線圖(International Roadmap for Devices and Systems, IRDS)接手 ,全面地反應各種系統級新技術。無論ITRS或是IRDS,均以技術節點(Technology Node)為具體化指標→表3。亦即以邏輯晶片的閘極長度(Gate Length),以及Dram的半間距(Half Pitch)為技術節點代表→圖8。並以此制定未來15年的發展,探討可能面臨的問題,並排序潛在的解決方案。

|

年份 |

Node |

晶圓尺寸 |

|---|---|---|

|

nm |

mm |

|

|

1980 |

2000 |

150 |

|

1989 |

900 |

150/200 |

|

1998 |

250 |

200 |

|

2001 |

130 |

200/300 |

|

2006 |

65 |

300 |

|

2013 |

28 |

300 |

|

2018 |

10 |

300 |

|

2019 |

7 |

300 |

圖8、Technology Node 示意圖

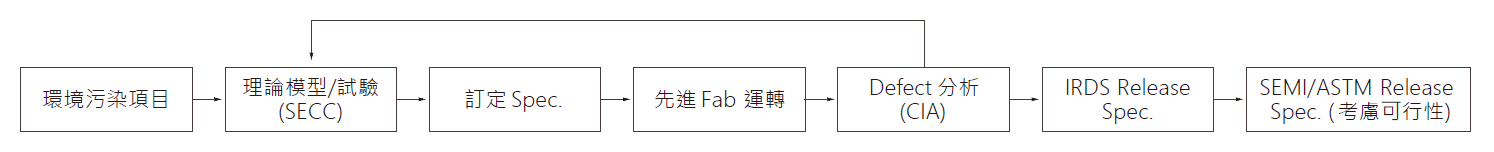

半導體廠務品質發展,自1999年11月起由ITRS於良率提升(Yield Enhancement, YE)章節內探討出版。良率提升章節(IRDS, 2016年)中,廠務品質標準訂定以「表面污染物控制(Surface Environment Contamination Control, SECC)」及「Defect分析檢測(Characterization, Inspection and Analysis, CIA)」兩大主題為訂定原則→圖9。每代技術節點的廠務品質是由表面污染物控制理論模型或試驗(SECC)訂出標準,輔以先進Fab運轉經驗中Defect分析檢測(CIA)回饋修正,最後由ITRS每兩年發表廠務品質標準,並交由SEMI考量可行性後,適時公布詳細規範 :

圖9、ITRS 良率提升章節中訂定廠務品質之基本流程

ITRS的表面污染物控制(SECC)模型,是由Defect作為限制式,進行模型推演或試驗得到品質標準,Defect成因主要分為物理、化學及漏電三類 :

物理性缺陷 [5][11][19]

- ITRS提及最關鍵指標為Particle Size,非帶電粒徑不可超過½技術節點,避免物理性的缺陷,而機台、空氣、氣體、UPW、化學品中的微粒、SiO2、細菌及金屬等等亦屬此類。

化學污染缺陷,分為直接與間接影響金屬及氧化層製程[3][13]

- 直接影響 : 液體中TOC及空氣中AMC直接沉降於晶圓表面,如式(1),進而影響氧化速率。來源為無塵室AMC、光阻殘餘、儲存容器、化學品。

N = C *(s×V×t)

N:晶片上的濃度,C:AMC濃度,s:粘附係數,V速度和暴露時間

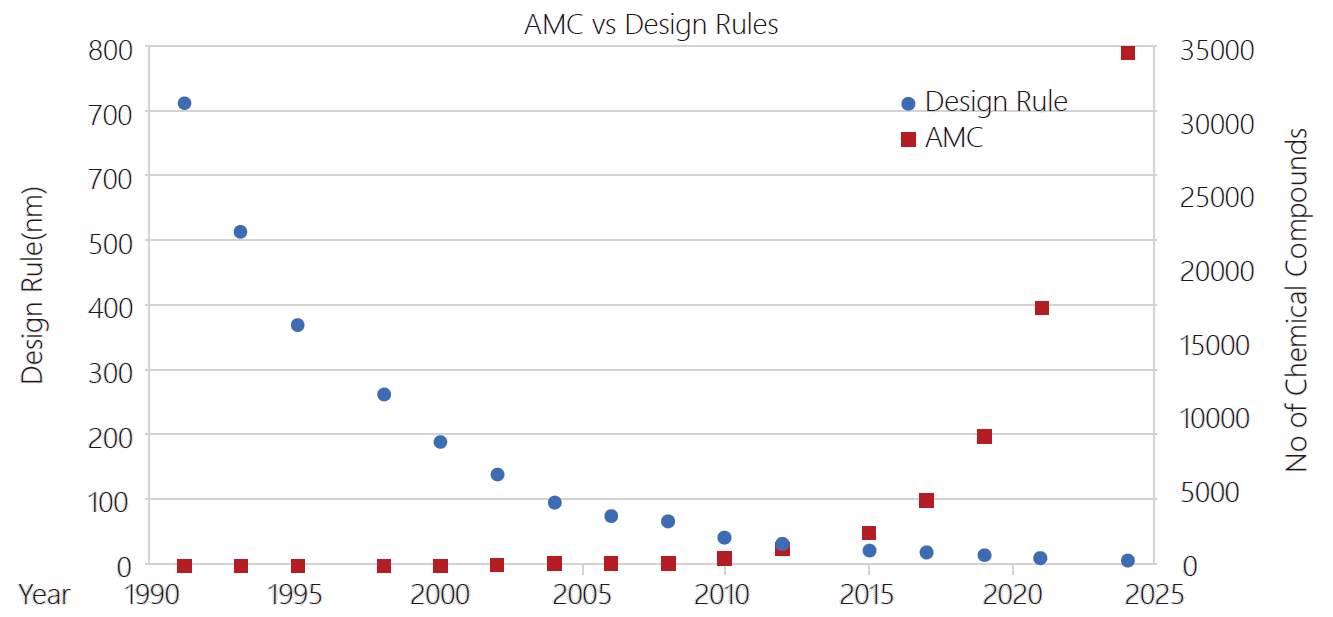

- 間接影響 : AMC會影響短波長曝光機的成像。以往8吋晶圓廠365nm曝光機並未有此困擾,但248nm曝光機時代,即發現對於氨氣(NH3)較為敏感。演進至193/157nm使用ArF及F2分子雷射,因波段極易受揮發性THC吸收,以及SO2/NO2因臭氧氧化造成鏡片霧化等困擾,故亦將AMC列為重要廠務品質之一→圖10。

圖10、技術節點演進-AMC管控圖

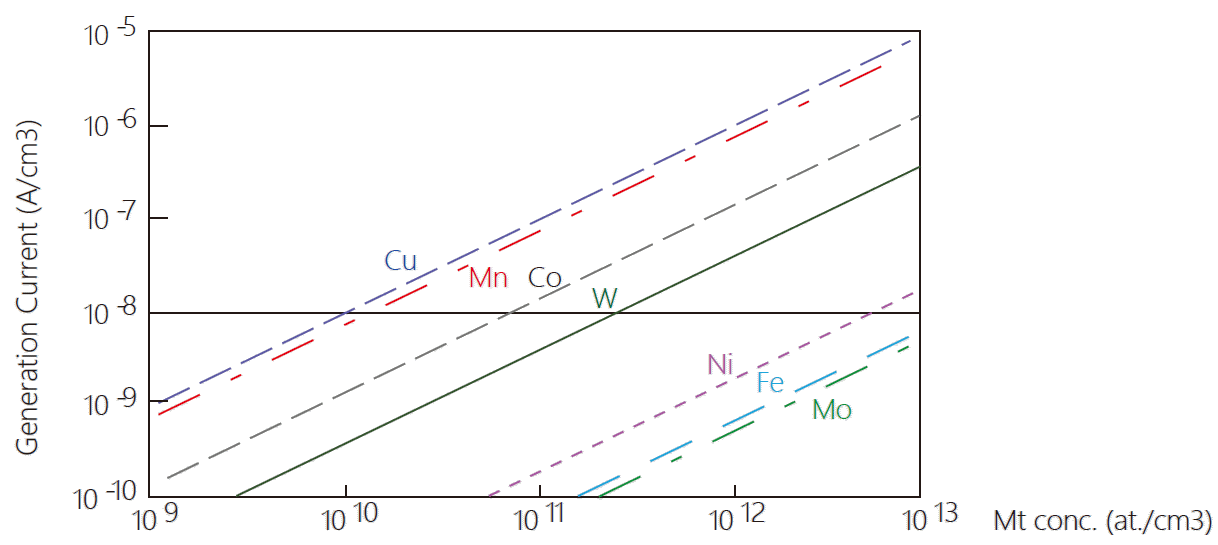

漏電缺陷,不純物導致漏電影響[8][13]

- 帶電微粒(Electrically Active Particle, EAP) : 粒徑為¼線寬時,因與金屬層距離過短有漏電疑慮。

- 陰陽離子 : 以技術節點所能允許的洩漏電流,訂定濃度標準→圖11。

圖11、濃度-電流圖 (以金屬為例)

總而言之,半導體廠務品質規範,皆根據技術線寬對照各種Defect的限制,訂定品質標準。以UPW為例,SEMI[5] 及ASTM[19] 規範皆以線寬差異,訂定各項水質標準→表4。

|

Reference |

ASTM D5127 |

SEMI F 63 |

||||||

|---|---|---|---|---|---|---|---|---|

|

Linewidth (microns) |

>5 |

5.0- 1.0 |

1- 0.5 |

0.35- 0.25 |

0.18- 0.09 |

0.065- 0.032 |

<0.065 |

|

|

Resistivity @ 25°C (MΩ·cm) |

12 |

16.5 |

18.1 |

18.2 |

18.2 |

18.2 |

>18.18 |

|

|

Particles (pcs/ml)@µm - online |

NA |

NA |

1@0.2 |

1@0.1 |

0.2@0.1 |

0.5@0.05 |

TBD |

|

|

Particles (pcsm/ml)@µm - offline |

10@1 |

3@0.5 |

NA |

NA |

NA |

NA |

||

|

Silica – Dissolved or Reactive |

NA |

NA |

3 |

1 |

0.5 |

0.5 |

<0.5 |

|

|

(µg/L), |

||||||||

|

Silica – Total (µg/L) |

50 |

10 |

5 |

3 |

1 |

0.5 |

||

|

TOC (ppb) |

300 |

50 |

5 |

2 |

1 |

1 |

<1 |

|

|

Dissolved Oxygen (ppb), |

NA |

NA |

25 |

10 |

3 |

10 |

<10 |

|

|

Bacteria (CFU/100 mL) |

50 |

10 |

5 |

3 |

1 |

ND |

<1 |

|

|

Ions (ppt) |

10000 |

1000 |

100 |

100 |

50 |

50 |

<50 |

|

|

Metals(ppt) |

Cu:2000 |

Cu:1000 |

50 |

20 |

20 |

10 |

<1~10 |

|

台積電先進封裝廠務品質管理模型

先進封裝的關鍵製程,重佈線層(RDL)為前段製程的技術延伸,根據半導體廠務品質發展的理論基礎,可以對照同等線寬的前段廠務品質,訂定先進封裝廠務品質標準。歸納上述結論,以技術、線寬及品質三個要素,建構先進封裝廠務品質管理模型→圖12:

圖12、先進封裝廠務品質管理模型

技術 :

以該製程的關鍵技術作為代表。

線寬 :

以該關鍵技術線寬作為代表。

品質 :

以該線寬參照半導體製程相同線寬,針對ITRS廠務品質項目(潔淨度、AMC、UPW、化學品及氣體供應)訂定建議標準。

應用先進封裝廠務品質管理模型,以甲製程及乙製程現況為例,提出廠務品質建議標準。甲製程的的關鍵技術及線寬為RDL的2μm;而乙製程在RDL技術未導入先進封裝廠製造的情況下,以μBump的10μm為關鍵技術及線寬,對照半導體廠務品質文獻:

潔淨度 :

半導體線寬10~1μm早於1990年代,無SIA及ITRS參考,以HDR Architecture[15]發表線寬及潔淨度歷史資料為參考依據。

UPW :

以美國材料和試驗協會(ASTM)D5127[5]為參考依據。

化學品及氣體 :

半導體線寬10~1μm早於1990年代,查無歷史文獻,建議以台積電6吋廠半導體製程相近線寬作為品質參考依據。

結果顯示,台積電先進封裝廠的甲製程及乙製程的廠務品質建議→表5。

|

Process |

製程甲 |

製程乙 |

|

|---|---|---|---|

|

關鍵技術 |

RDL |

*RDL |

Microbump |

|

關鍵技術線寬 (µm) |

2 |

0.5 |

10 |

|

Wafer Environment Control |

|||

|

Reference 線寬(µm) (半導體發展) |

2 |

0.5 |

2 |

|

Number of particle (ISO CL) |

6 |

3 |

6 |

|

UltraPure Water |

|||

|

Reference 線寬(µm) (ASTM D5127) |

5-1 |

1-0.5 |

>5 |

|

Resistivity @ 25°C (MΩ·cm) |

16.5 |

18.1 |

12 |

|

Particles (pcs/ml)@µm |

3@0.5 |

1@0.2 |

10@1 |

|

Silica (ppb as SiO2) |

10 |

NA |

50 |

|

TOC (ppb) |

50 |

3 |

300 |

|

Dissolved Oxygen (ppb) |

NA |

5 |

NA |

|

Bacteria (CFU/100 mL) |

50 |

5 |

250 |

|

Ions (ppt) |

1000 |

25 |

10000 |

|

Metals (ppt) |

**Cu:1000 |

5 |

**Cu:2000 |

* 製程乙RDL由半導體廠製造 ** Metals濃度標準僅管制Cu離子標準

台積電先進封裝廠務品質藍圖

先進封裝未來發展趨勢

未來的先進封裝將具有不同的2D和3D結構,扇出型封裝將往大尺寸封裝前進,覆晶封裝則相反,朝小尺寸封裝發展。工業技術研究院產業科技國際策略發展所產業分析師楊啟鑫[2]也分析,未來五年扇出型封裝將逐漸走向多晶片系統級封裝(System in Package, SIP),同時扇出型封裝亦朝向高密度(High I/O Density),亦即細線寬的重佈線層(RDL)發展,並朝向更大的扇出型多晶片系統級封裝發展。但封裝面積大於40*40mm²之封裝將仍以覆晶封裝為主,而覆晶封裝之載板亦朝向細線寬線的RDL發展。未來十年後,多晶片系統級扇出型封裝(SiP),已逐漸可與覆晶封裝技術競爭,而在高密度扇出型封裝逐漸發展成熟趨勢下,將嚴重侵蝕覆晶封裝市場。

先進封裝不論是覆晶或扇出型封裝,除系統級封裝(SIP)的發展方向外,更細線寬的RDL為另一發展目標,而RDL線寬發展也有所區別,分為半導體製造後段製程(Back End Of Line, BEOL)以及先進封裝廠製造,線寬分別為

1~0.5μm及10~2μm。屬於覆晶封裝的乙製程,RDL為0.5μm在半導體廠(BEOL)製造,而屬於扇出型封裝的甲製程,RDL為2μm則在先進封裝廠製造。

此外,對於先進封裝廠RDL的未來發展,KLA-Tencor資深副總Oreste Donzella於SEMICOM Taiwan 2018年的公開演說中表示,KLA-Tencor發現許多客戶的技術藍圖上,已經存在5μm、甚至2μm線寬技術,進而推論RDL線寬或許會成為下個摩爾定律。實際上,台積電也於2018年IEEE上發表第一個次微米(0.8μm)RDL線寬的InFO製程技術,稱之為InFO_UHD(Ultra-High-Density),並持續朝0.4μm發展。半導體工程雜誌Mark Lapedus[15]更預測2020年先進封裝廠將引進半導體後段製程(BEOL)技術使1μm問世。以此推估未來15年先進封裝的技術發展趨勢,每3年線寬微縮一半,也符合先進封裝每3年為一個產品的生命週期→表6。

|

Year of Production |

2016 |

2018 |

2021 |

2024 |

2027 |

2030 |

2033 |

|---|---|---|---|---|---|---|---|

|

Pitch : RDL線寬(µm) |

10 |

2 |

1 |

0.5 |

0.25 |

0.13 |

0.065 |

|

1/2 Pitch : 50%線寬(µm) |

5 |

1 |

0.5 |

0.25 |

0.13 |

0.065 |

0.033 |

|

該Node半導體年份 |

1980 |

1987 |

1997 |

2001 |

2007 |

2013 |

|

|

曝光機世代(nm) |

G (436) |

I (365) |

DUV (248) |

ArF (193) |

|||

台積電先進封裝廠務品質發展藍圖

技術藍圖是指以簡單的方式,對未來技術發展之基本表述,具有高度概括、高度綜合和前瞻性的基本特徵。半導體行業的摩爾定律,每18個月半導體密度增加一倍,就是基於半導體技術發展藍圖的表述[18]。摩爾定律的意義不只是描述了一種現象,在半導體開發技術過程中,也對相關企業明示應該開發的具體技術和達成期限,以集中業界資源。

技術藍圖的制定過程,是組織利益相關者,對未來領域發展形成共識並表達出來的過程,也使得不同領域的人,但為相同目標努力的人相互理解,它將分散的信息整合到一個平臺上供大家共同使用。

歸納文獻,將技術藍圖的制定過程大致分為四個步驟[9][10] :

準備階段 :

確定技術藍圖的方法論,收集相關文獻、確定利益相關人、形成對技術發展和應用的初步分析。制定和修訂的參與者要涵蓋該領域的利益相關人。

未來發展趨勢分析 :

分析技術現狀、各種條件及面臨的障礙,確定未來發展的目標和時間框架。

技術發展路線 :

為實現預期目標,根據技術發展狀況和現實條件,確定優先發展方向,描述研究項目。

技術藍圖回饋 :

對實施效果進行第三方評價,作為管理部門決策的依據。

總結前述研究,可以應用技術藍圖制定的步驟,搭配台積電先進封裝廠務品質管理模型,及先進封裝技術未來15年的發展趨勢,建構2018年至2033年台積電先進封裝廠務品質藍圖,說明如下 :

第一、

準備/未來發展趨勢分析階段 : 先進封裝以覆晶及扇出型封裝為發展主流,四大領域需求面對成本問題,除多系統封裝(SIP)外,縮小細線寬重佈線層(RDL)為主要發展方向,但先進封裝廠務品質隨著製程微縮,並無類似半導體技術發展藍圖(ITRS)可參考,必須發展先進封裝廠務品質藍圖,進而建構系統化的廠務品質管理。

第二、

技術發展路線階段 : 蒐集先進封裝技術發展現況及未來趨勢,以RDL線寬為關鍵技術,參照半導體廠務品質發展文獻。建構先進封裝廠務品質發展藍圖,規範內容包含:

- 關鍵技術 : 先進封裝技術以RDL之線寬最具代表性。

- 線寬趨勢 : 每3年線寬微縮一半,推估未來15年先進封裝的技術發展趨勢。

- 品質標準 : 參照半導體製程相同線寬,針對ITRS廠務品質項目(潔淨度、AMC、UPW、化學品及氣體供應)訂定建議標準。因半導體線寬10~1μm早於1990年代,除UPW品質可參考ASTM,及潔淨度可參考HDR architecture外,其他廠務品質無歷史文獻可供參考,建議以台積電6吋廠半導體製程相近線寬所制訂OOC作為品質參考依據。

第三、

技術藍圖回饋 : 由利害相關專家進行模型回饋及驗證,每3年修正一次。

依上述規範建構未來15年台積電先進封裝廠務品質藍圖→表7。

|

現況 |

台積電先進封裝廠務品質管理模型 |

||||||

|---|---|---|---|---|---|---|---|

|

Year of Production |

封測A廠 |

2018 |

2021 |

2024 |

2027 |

2030 |

2033 |

|

RDL 線寬, µm |

2 |

2 |

1 |

0.5 |

0.25 |

0.13 |

0.065 |

|

Node, 1/2 Pitch, µm |

1 |

1 |

0.5 |

0.25 |

0.125 |

0.065 |

0.033 |

|

Ref. from ITRS or SIA |

1997 |

2001 |

2007 |

2013 |

|||

|

曝光機, nm |

I, 365 |

I, 365 |

DUV, 248 |

ArF, 193 |

|||

|

Wafer Environment Control |

|||||||

|

wafer接觸之微粒等級, ISO CL |

5 |

6 |

4 |

2 |

2 |

2 |

1 |

|

AMC in Gas Phase - Lithography, cleanroom ambient |

|||||||

|

酸 , as SO4, ppbV |

3 |

AMC不影響365nm 曝光機反應 |

NA |

NA |

5 |

5 |

|

|

鹼 , as NH3, ppbV |

21.5 |

50 |

50 |

50 |

50 |

||

|

冷凝有機物, ppbV |

NA |

NA |

NA |

26 |

26 |

||

|

高極性物質, ppbV |

NA |

0.1 |

0.1 |

0.1 |

0.1 |

||

|

晶圓表面有機物(SMC), ng/cm2/day |

NA |

NA |

NA |

2 |

2 |

||

|

UltraPure Water |

|||||||

|

Resistivity @ 25°C (MΩ·cm) |

18 |

16.5 |

18.1 |

18.2 |

18.2 |

18.2 |

18.2 |

|

Particles (pcs/ml) @µm |

5 @0.2 |

NA |

1@0.2 |

1@0.1 |

0.2@0.1 |

0.5@0.05 |

0.2@0.05 |

|

Silica – Dissolved or Reactive (ppb as SiO2) |

5 |

NA |

3 |

1 |

0.5 |

0.5 |

0.3 |

|

TOC (ppb) |

90 |

50 |

5 |

2 |

1 |

1 |

1 |

|

Dissolved Oxygen (ppb) |

100 |

NA |

25 |

10 |

3 |

10 |

10 |

|

Bacteria (CFU/100 mL) |

5 |

10 |

5 |

3 |

1 |

1 |

1 |

|

Ions (ppt) |

200 |

NA |

100 |

100 |

50 |

50 |

50 |

|

Metals (ppt) |

200 |

Cu:1000 |

50 |

20 |

20 |

10 |

1 |

|

Liquid Chemicals |

|||||||

|

49% HF, 37% HCl, pcs/ml |

NA |

6吋廠 OOC為標準 |

10 |

10 |

10 |

3 |

|

|

30% H2O2, 29%NH4OH, 100%IPA, pcs/ml |

NA |

1000 |

1000 |

1000 |

300 |

||

|

49% HF Cl, ppb |

500 |

NA |

NA |

10 |

10 |

||

|

Critical Metal, ppt |

1000 |

500 |

150 |

150 |

150 |

||

|

Non Critical Metal, ppt |

1000 |

1000 |

500 |

500 |

500 |

||

|

Bulk Gases (Contaminants, ppbv) |

|||||||

|

N2 (O2, H2, H2O, CO, CO2, THC) |

2 |

6吋廠 OOC為標準 |

5 |

5 |

5 |

5 |

|

|

O2(N2, Ar) |

2 |

50 |

50 |

50 |

50 |

||

|

O2(H2, H2O, CO, CO2) |

2 |

10 |

10 |

10 |

10 |

||

|

Ar (O2, H2, H2O, CO, CO2) |

NA |

5 |

5 |

5 |

5 |

||

|

H2(O2, H2O, CO, CO2) |

NA |

10 |

10 |

10 |

10 |

||

|

He (O2, H2, H2O, CO, CO2) |

NA |

NA |

NA |

10 |

10 |

||

|

CO2 (O2, H2O, CO) |

NA |

NA |

NA |

1000 |

1000 |

||

結果顯示,隨著製程推進,未來將面臨兩個問題:

第一、

當品質建議標準小於OOC時,OOC須進行Tighten。以封測A廠為例,2019年線寬為2μm,UPW TOC 建議標準為50ppb小於目前的OOC 90ppb,須進行OOC Tighten。

第二、

當品質建議標準小於Baseline時,須進行廠務品質提升。假設封測A廠製程持續推進,2024年線寬將達0.5 μm,部分廠務供應品質無法滿足製程需求,以UPW TOC為例,品質建議標準為2ppb,已小於目前的Baseline,則須進行廠務品質提升。

另一方面,研究指出曝光機波長低於365nm(i-line)時,AMC將影響製程品質。2024年線寬達0.5μm時,將開始使用248nm波長的DUV曝光機,屆時AMC須納入廠務品質管制。

品質管理模型驗證

品質藍圖發展制定流程中,須涵蓋該領域的利益相關人,且對實施效果進行第三方回饋,作為管理部門決策的依據。以下提供兩個實際案例作為模型驗證。

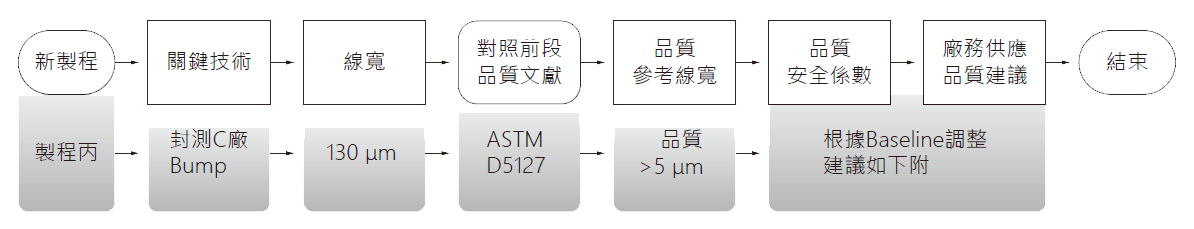

案例1、封測C廠丙製程品質訂定

以封測C廠的丙製程廠務品質案例,作為品質管理模型的實例驗證。在2018/09/06 封測C廠的丙製程相關Utility Spec. 及訂定後段O.I.規範討論會議上,與利害相關專家,後段製程整合、後段製程、廠務、後段品質管理中心主管達成共識,依照台積電先進封裝廠務品質管理模型,訂定封測C廠的丙製程UPW品質標準。管理模型決策流程→圖13。

圖13、先進封裝廠務品質管理模型 – 丙製程決策流程

以丙製程的Bump為關鍵技術代表,其代表線寬為130μm,對照ASTM D5127前段製程同等線寬的UPW品質標準 ,可以得出建議水質→表8。

|

Site |

Process |

關鍵技術 |

品質標準 |

線寬 |

Resistivity |

Particles |

Silica |

TOC |

Dissolved Oxygen |

Bacteria |

Ions |

Metals |

|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

µm |

25°C (MΩ·cm) |

pcs/ml |

ppb |

ppb |

ppb |

CFU/100 mL |

ppt |

ppt |

||||

|

封測C廠 |

製程丙 |

Bump |

建議 |

>5 |

12 |

10@1µm |

50 |

300 |

NA |

250 |

10000 |

Cu:2000 |

|

現況 |

130 |

17.5 |

5@0.2µm |

5 |

90 |

100 |

5 |

200 |

200 |

案例2、乙製程引進封測A廠品質訂定

2019/07/26原於十二吋晶圓廠生產製造之乙製程引進封測A廠,先進封裝品質管理中心(APMEP)要求廠務進行品質規範比對,但因母廠廠務品質規範是專為十二吋晶圓製造而訂定,非為乙製程量身打造,品質規範優於封測A廠 ,且已超出封測A廠廠務系統的供應能力。因此,依照台積電先進封裝廠務品質管理模型建議品質標準,乙製程關鍵技術為22μm的μBump,而既有封測A廠關鍵技術為甲製程2μm的RDL。乙製程引進封測A廠後,封測A廠的關鍵技術不變,故建議維持現行廠務品質標準,此建議也獲得客戶及品質管理中心的同意。

結論

目前先進封裝的廠務品質標準訂定並無類似國際半導體技術發展藍圖可供參考。台積電作為先進封裝業的先行者 ,同時兼具半導體製造經驗的競爭優勢,可以參考半導體的發展經驗,配合先進封裝製程特性,並根據建構技術路線圖的4個階段,自行發展先進封裝廠務品質藍圖,進而建構系統化的先進封裝廠務品質管理。

先進封裝的關鍵製程,重佈線層(RDL)為前段製程的技術延伸,因此根據半導體廠務品質發展的理論基礎,可以對照同等線寬的前段廠務品質,訂定先進封裝廠務品質標準。以技術、線寬及品質三個要素,建構先進封裝廠務品質管理模型。

總結研究,每三年RDL線寬微縮一半,推估未來15年的技術發展趨勢,並透過品質管理模型,參照ITRS廠務品質文獻,建構先進封裝廠務品質發展藍圖,未來每三年更新一次。

品質藍圖發展制定流程中,也涵蓋該領域的利益相關人,且對實施效果進行第三方回饋,作為管理決策的依據。經過封測C廠丙製程品質訂定及乙製程引進封測A廠品質訂定兩個實際案例作為模型驗證。

本模型除與製程及先進封裝品質管理中心專家達成共識外,模型有效性也獲工廠及客戶得高度認同,並非一昧以前段母廠Pilot Line的高品質要求為最佳策略,從根本回應前段母廠與後段製程產品不同,品質標準亦毋須相同的問題,開始為後段製程量身打造廠務品質標準。

最後,台積電對內根據SPC二階O.I.定義,廠務品質規範每年須進行Control Limit Review。既有的Review Rule是根據統計檢定及管理效率觀點進行Control Limit Tighten,並非根據生產品質的實際需求。沒有高度相關的理論依據,持續提高廠務品質標準,造成廠務運轉成本逐年上升。先進封裝品質管理中心建議,將此先進封裝廠務品質發展藍圖納入SPC O.I. 正式規範,以與生產品質高度相關的廠務品質標準,取代統計檢定的管理方式,除了避免廠務運轉成本提高外,也可作為澄清產品Defect的廠務品質標準依據。

參考文獻

- 胡承維,CoWoS & Fan-Out Process Flow,2017。

- 楊啟鑫,電子終端產品暨先進封裝未來發展趨勢分析,2018。

- 劉興學,應用化學濾網去除某晶圓廠黃光區潔淨室的氨氣 (博士論文),2008。

- ASE, ASE FOWLP Roadmap, 2017.

- ASTM, Standard Guide for Ultra-Pure Water Used in the Electronics and Semiconductor Industries (D5127), 2018.

- C.P. Wong, Materials for Advanced Packaging (2nd), 2016.

- Douglas Yu, iMAPS DPC, 2012.

- Drew Sinha, & Slava Libman, Metals Spec in UPW, White Paper, 2015.

- Hilary Martin, Technology roadmap development process for the service sector, 2012.

- IEA, Technology Roadmap A guide to development and implementation, 2014.

- IRDS, Yield Enhancement White Paper, 2016.

- IRDS, Yield Enhancement, 2017.

- ITRS, International Technology Roadmap for Semiconductors, 2002; 2005.

- John H Lau, Fan-Out Wafer-Level Packaging for 3D IC Heterogeneous Integration, 2018.

- Mark Jamison, 300mm Wafer Fab Contamination Control, 2011.

- Mark Lapedus, Challenges For Future Fan-Outs, 2017.

- PSMC, Technology Roadmaps What Value for PSMC?, 2013.

- Ronald N. Kostoff, Science and Technology Roadmaps, 2001.

- SEMI, Guide For Ultrapure Water Used In Semiconductor Processing(F063), 2018.

- SIA, Semiconductor Research Opportunities: An Industry Vision and Guide, 2017.

- Warren W. Flack, One micron redistribution for fan-out wafer level packaging, 2017.

- XLINX, CoWoS Process Flow, 2013.

- Yole Development, The advanced packaging industry is on the move, 2018.

- Yuanta, Fan out InFO, 2016.

- Zhang et al., Appl. Phys. Rev. 2, 2015.

- Warren W. Flack et al., One Micron Redistribution for Fan-Out Wafer Level Packaging, 2017.

留言(0)